# Voice Recorder

Ben Wolsieffer and Afia Semin ENGS 31 - 18 X

## Abstract

This project is a voice recorder that captures audio from an onboard microphone and plays it back through a speaker. Audio data is stored on an SD card, allowing for long recording times and long-term storage. It is also possible to write an audio file to the SD card from a computer and play it back using the voice recorder. The recorder was implemented on a Xilinx Artix-7 FPGA using the Digilent Basys 3 development board, as a well as a variety of Digilent Pmods.

# Table of Contents

| 1. Introduction                                |     |

|------------------------------------------------|-----|

| 2. Design solution                             | 4   |

| 2.1. Specifications                            | 4   |

| 2.2. Operating Instructions                    | 4   |

| 2.3. Theory of Operation                       | 5   |

| 2.4. Construction and Debugging                | 10  |

| 3. Evaluation                                  | 11  |

| 4. Conclusions                                 |     |

| 5. Acknowledgments                             | 12  |

| 6. References                                  | 13  |

| Appendix A - Annotated front panel             | 14  |

| Appendix B - Block diagrams                    | 15  |

| Appendix C - State diagrams <sup>1</sup>       | 22  |

| Appendix D - Parts list                        | 27  |

| Appendix E - VHDL code and constraints         | 28  |

| Appendix F - Resource utilization              | 98  |

| Appendix G - Residual warnings                 | 100 |

| Appendix H - Memory map                        | 101 |

| Appendix I - Simulation waveforms <sup>1</sup> | 102 |

| Appendix J - Computer program                  | 106 |

<sup>&</sup>lt;sup>1</sup> To see enlarged versions of the diagrams in this appendix, click on the images.

## 1. Introduction

The primary objective of this project was to create a digital voice recorder that was capable of recording audio from a microphone, storing it and then playing it back through a speaker. An additional goal after accomplishing the primary goal was to store the audio on an SD card, allowing much longer recording times.

### 2. Design solution

#### 2.1. Specifications

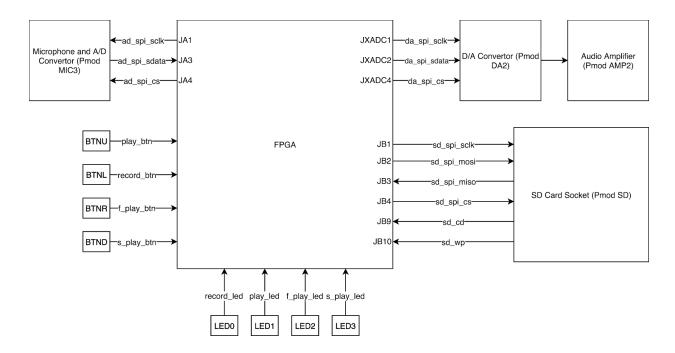

This system is a voice recorder that records audio from an onboard microphone and stores it onto an SD card. It is also capable of playing back audio from the SD card. The voice recorder uses the onboard LEDs and pushbuttons of the Basys 3 for its user interface. It uses a Pmod MIC3 connected to port JA for audio input, and a Pmod DA2 connected to port JXADC to generate an analog audio signal. The analog signal is passed through an adapter board to a Pmod AMP2 audio amplifier, which drives a speaker. Finally, an SD card socket (Pmod SD) is attached to port JB. A photograph of this setup is shown in Appendix A. The connections and internal pin mappings between the FPGA and Basys 3 ports are shown in Figure B1.

#### **2.2. Operating Instructions**

To operate the system, the Pmods must be connected as described in the specifications section and shown in the front panel diagram (Appendix A). An SD card must be inserted in the

socket before the system is powered on. If the SD card is removed while the system is on, the card must be reinserted and the system must be restarted before it can be used. To begin a recording, press the record button. To stop the recording, press the record button again. The recording can be played back at a chosen speed using any of the play buttons. The recording will play until it is finished, or the same button is pressed again. The row of lights along the bottom of the board allows the user to determine the current state of the system. The SD card driver respects the write protect switch on the SD card. If the record LED does not turn on after the record button is pressed, make sure the write protect switch is in the unlocked position.

#### **2.3.** Theory of Operation

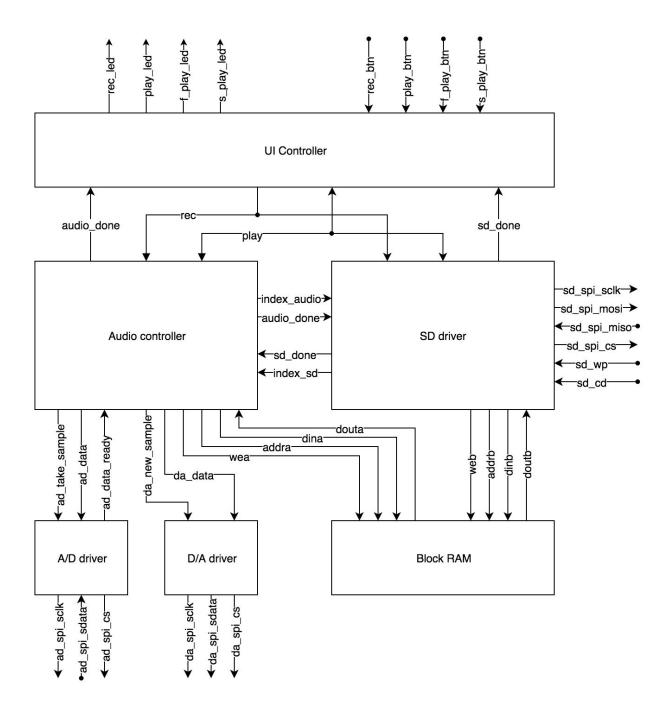

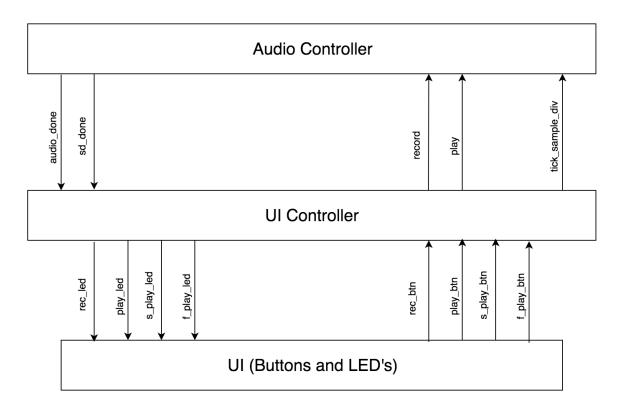

The main components of the system are the UI controller, the audio controller, and the SD card driver, as well hardware interface components for the A/D and D/A convertors (their connections are shown in Figure B2).

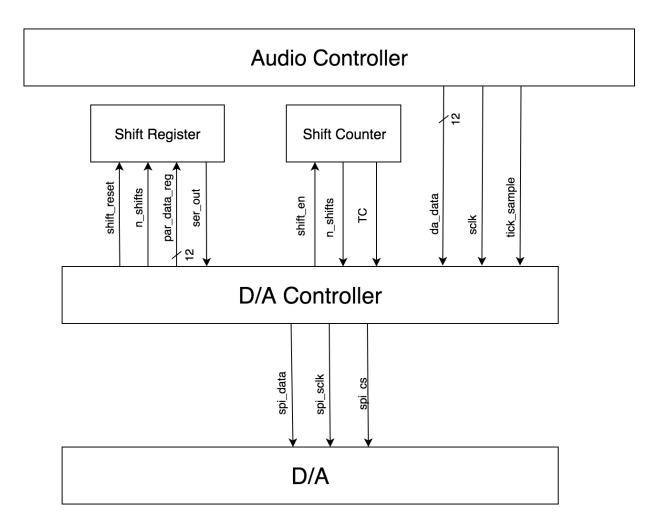

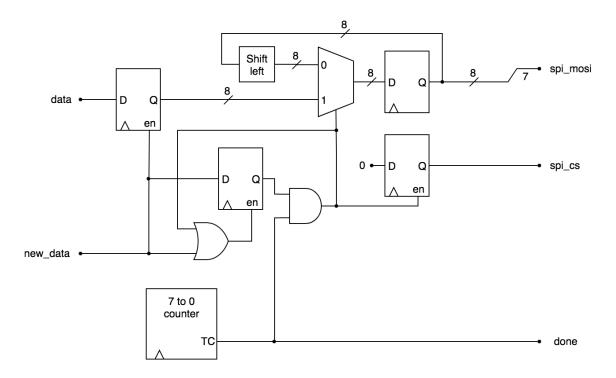

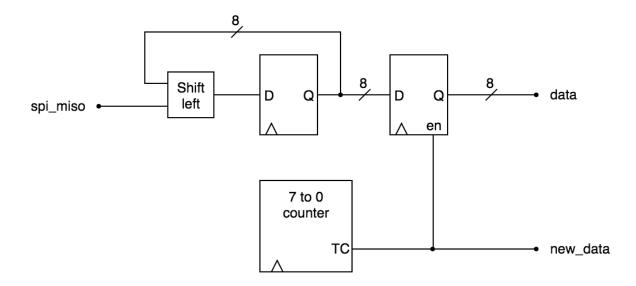

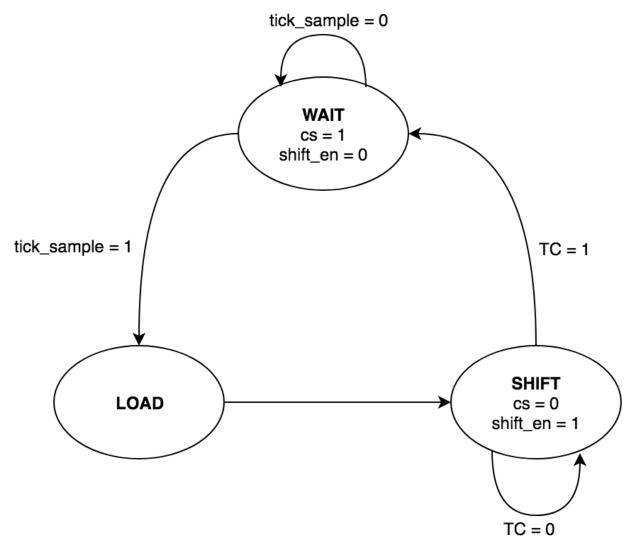

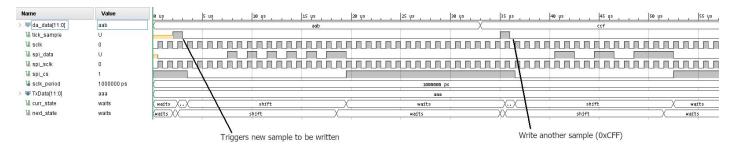

Audio is recorded with a Pmod MIC3, which uses a Texas Instruments ADCS7476 A/D convertor, and audio is played using a Pmod DA2 with a Texas Instruments DAC121S101 D/A convertor. The driver for the Pmod MIC3 is identical to the one used in the last two labs, except for the addition of a done signal that is asserted as the last bit is shifted in. The Pmod DA2 driver is similar to the A/D driver, except it is a parallel to serial shift register instead of a serial to parallel shift register (see Figure B3 and C1).

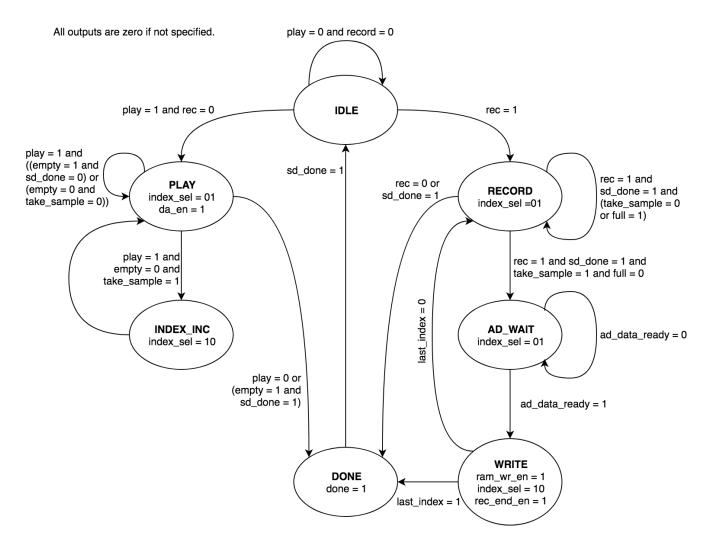

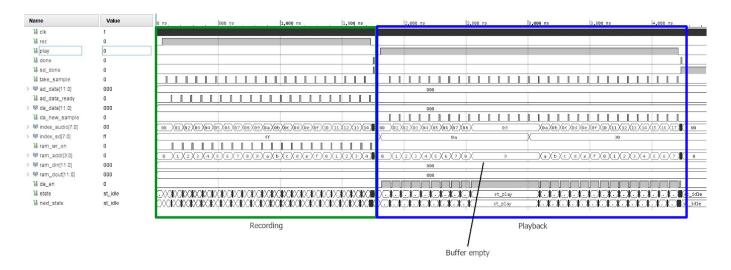

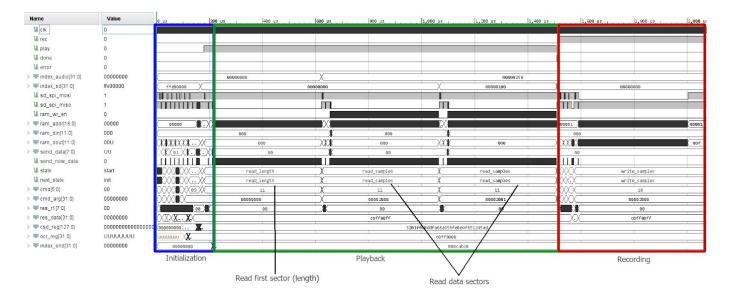

The A/D and D/A drivers are connected by the audio controller. The audio controller is a finite state machine (described in Figure C2) that outputs a take sample pulse at the audio sample rate (specified by the UI controller). This signal is continuously passed to the A/D driver, even during playback, but it is gated by an enable signal before being passed to the D/A driver to

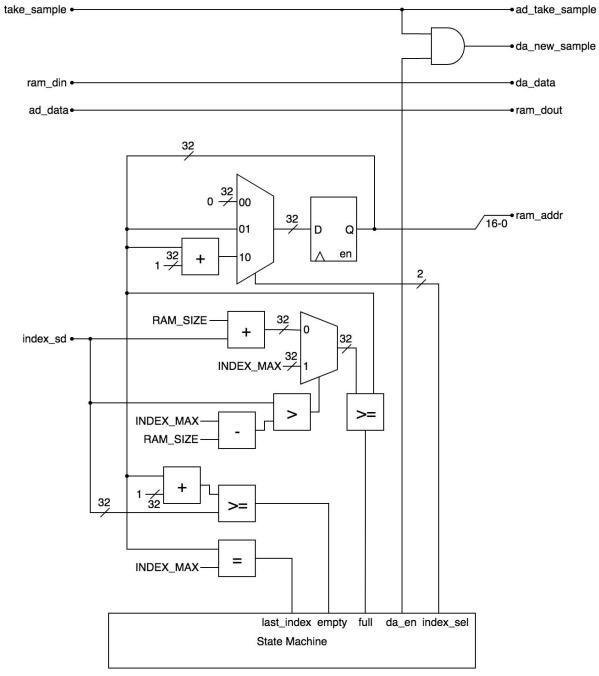

prevent unwanted noises from being played by the D/A while recording. The audio controller is also responsible for writing the A/D and D/A data to and from the RAM buffer. It receives the current position in the RAM buffer from the SD card driver and uses it to decide whether there is enough data in the circular buffer to continue playback, and also whether the buffer is full while recording (see Figure B4 for details of the bounds checking). The circular buffer and bounds checking are implemented using a monotonically increasing counter that represents the number of samples that have been played or recorded. The SD driver has its own version of this counter, which keeps track of how many samples it has read or written. The actual position in the RAM is the sample index modulo the RAM size. The RAM size is configured to be a power of two (in this case, 131,072 or 2<sup>17</sup>), which turns the modulus operation into an efficient bit mask. The sample index is used in the comparison operations, which makes it unnecessary to explicitly determine when the circular buffer wraps.

Data in the circular buffer is transferred to an SD card for permanent storage. SD cards have two modes of communication, a native high-performance protocol using four data lines, and a simpler SPI mode. Communication is symmetrical, with both the master and slave (SD card) shifting out data on the falling edge of the clock and latching data on the rising edge. The master initiates all communication.

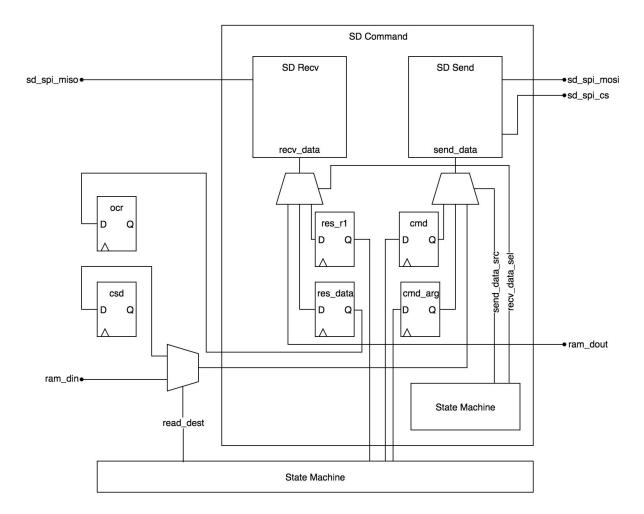

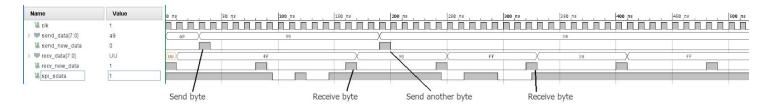

In this design, the SD card driver has the minimum possible interaction with the audio components of the system. The SD driver consists of three levels of components, starting at the lowest level with a pair of components that constantly send and receive from the SPI bus in 8-bit increments. The SD protocol operates on the byte level, so the smallest unit the higher-level components of the driver will have to work with is one byte (8 bits). The sending and receiving components operate as parallel to serial and serial to parallel shift register convertors, respectively. These components are always shifting, and they assert a signal as the last bit is being shifted out or in. In addition, the sending component has a signal that causes an input to be stored into the parallel register. When there is no data to send, the bus is held high (ones are shifted out), which indicates that it is idle. The SD card also holds its master-out-slave-in (MOSI) line high when idle, making it possible to detect traffic on the bus by waiting for a received byte that is not equal to 0xFF (the first byte of any transfer is guaranteed to have at least one zero). The sending component is also responsible for asserting chip select (CS) when the first data is sent. This is done at such a low level because CS serves as the framing signal for the data, and must occur as the first bit is sent. The higher-level components of the driver do not operate at the bit level, making it difficult for them to accomplish this precise timing. In this implementation, the CS signal is never deasserted, because the SD cards tested were able to maintain their framing without it. There is anecdotal evidence (web comments) that some cards require CS to be deasserted and asserted between commands. The detailed design of these components is shown in Figures B6 and B7.

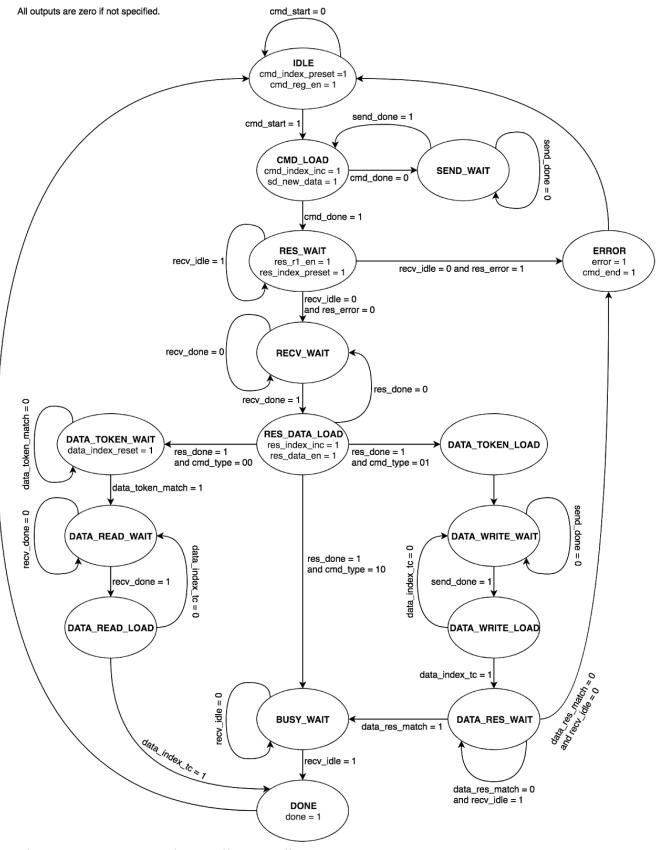

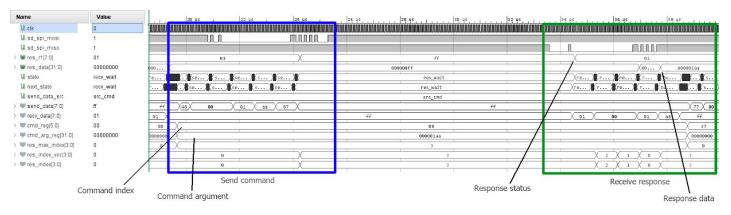

Above the sending and receiving components is the command driver, which executes commands and returns their responses. It is implemented as a finite state machine (FSM), fully described in Figure C5. When a start signal is asserted, the state machines registers a command index and argument, sends it to the card, waits for a response and then asserts a done signal. Most commands have a short response ranging from 1 byte to 5 bytes. The first byte always has the same format, and indicates whether an error occurred. Certain commands, in particular those that read from the card, send a second response that contains the data that was read. While the driver returns the first response as a 32 bit signal, the second response is returned as a single byte and an index that increments as the response is read. This makes it easy to directly map this data into RAM. Data writes are performed using a similar mechanism in the opposite direction, with the master sending a data block after receiving the first response from the card.

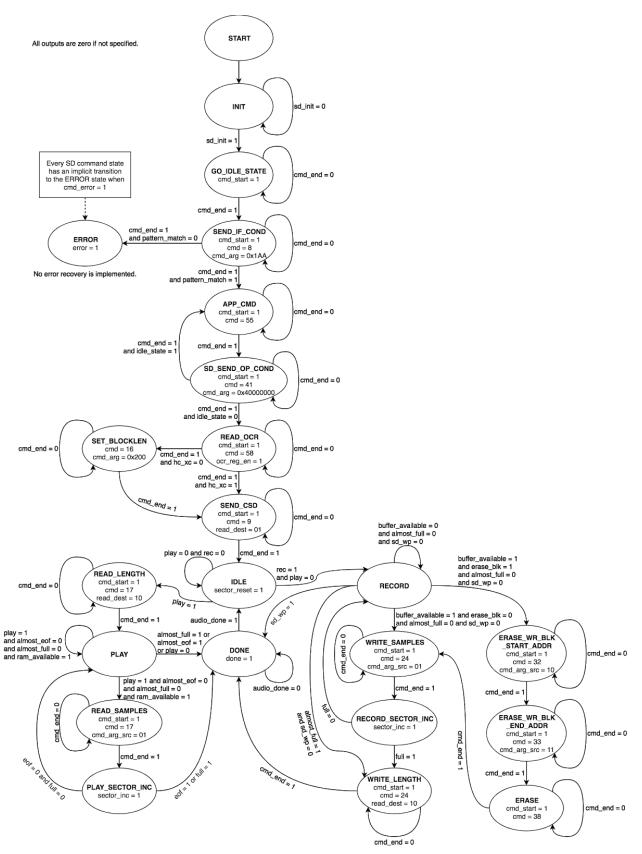

The highest level of the SD card driver manages the sequencing of commands during initialization, as well as the transfer of data between the audio RAM and the SD command driver. The SD card driver is also an FSM, with many states named after SD command mnemonics (described in Figure C5, the state diagram for the SD card driver, and B8, which is an abbreviated version of the block diagram for the command controller and the card driver; a more complete block diagram for this part of the project is not available due to complexity and time constraints). The SD card standard has gone through several revisions, and therefore a fully compatible driver must perform different commands and checks depending on which version of the standard a particular card implements. To make implementation simpler, only SD version 2 and greater cards were supported. In addition, only SDHC and SDXC cards (which use sector addressing) were available to test, so support for standard capacity SD cards (which use byte addressing) is only theoretical. Data transfers are performed using single block read and write commands. While using multiblock data transfer commands would have been more efficient, there was not sufficient time to implement them. This is particularly true for writing, as a naive single block writing algorithm suffers from the FLASH write amplification issue. FLASH memory must be erased before it can be written, and the minimum size that can be erased is much larger than the minimum size that can be written. Therefore, to change a single byte, it is necessary to buffer the entire erase block, erase it and then write the data back with the single

byte changed. This reduces performance and can cause premature failure of the FLASH device because FLASH can only withstand a limited number of erase cycles. Multiblock writes work around this problem by making it possible for the SD card firmware to buffer many writes before erasing a block. A possibly simpler solution is also available, because the SD protocol allows sectors to be explicitly erased. In the case of the voice recorder, a new recording overwrites an old recording, making it possible to preemptively erase a large block ahead of the recording. The SD driver implements these commands, erasing 4 MiB blocks ahead of the current recording position. It is possible to determine the exact erase block size of a particular card, but this was not done due to time constraints.

The driver implements minimal error checking and recovery. Error codes or unexpected values in command responses are detected, but no attempt is made to recover. The driver simply stops in the case of errors. Timeouts are not implemented, meaning that if a card is disconnected in the middle of a command, the driver will hang. The SD protocol optionally uses a cyclic redundancy check (CRC) to verify the integrity of commands and data, but this is not implemented by this driver beyond the first few initialization commands that require it. Rather than calculating a CRC, hardcoded values are used because the contents of the commands are fixed.

The SD driver interacts with the audio components through the block RAM as well as an index that indicates which sample of the audio file is currently being recorded or played. The SD driver only writes during recording when there are at least 512 bytes (one sector) buffered in the RAM, and only reads during playback when there are at least 512 bytes free in the circular buffer.

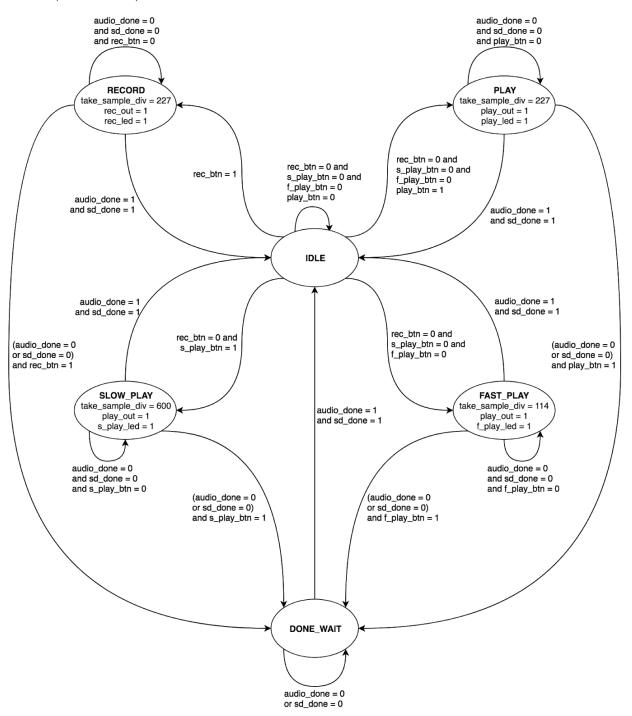

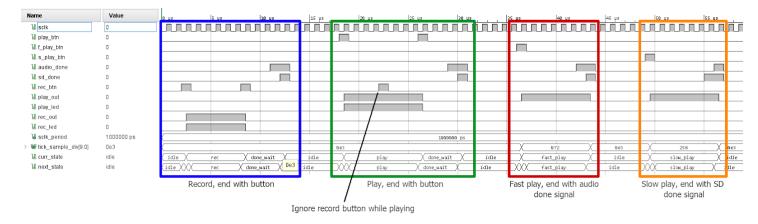

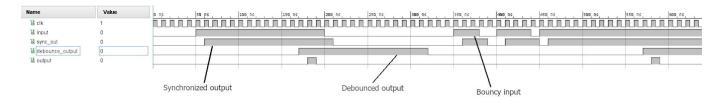

The high-level state of the system is controlled by the user interface (UI) controller. It takes the debounced monopulsed buttons as inputs and produces record and play signals as outputs. In addition, it has two inputs from the audio controller and SD driver that indicate that they are done (either after the recording or after playback was stopped manually, or the end of the file was reached). If the UI controller is in the idle state and one of the buttons is pressed, it transitions to the corresponding state, and asserts either the play or record output. It remains in that state until the same button is pressed again, or either the audio controller or SD controller indicates that it is done. In either case, it waits for both done signals to be asserted before returning to the idle state. The audio controller and SD driver also wait for their counterparts' done signals, which synchronizes the three major components of the system. To implement the fast and slow play capabilities, the UI controller outputs a signal that controls the speed of the take sample pulse. The full state diagram and block diagram can be seen in Figures C3 and B5, respectively.

#### **2.4.** Construction and Debugging

The first components that were designed and implemented were the drivers for the A/D and D/A convertors. The A/D convertor driver was already written for the last few labs, so it was simply modified to include a done signal that is asserted as the last bit is shifted in. Once these components were written and tested in simulation (see Appendix I for simulation waveforms), a simple demo system was created that simply forwarded data from the A/D to the D/A. This worked on the first try, except for an issue with a different pin mapping between the Pmod AD1 and the Pmod MIC3. The next step was to implement the system that would accomplish the first design goal. This was the design presented at the design review. This system worked with few issues, other than a strange problem where the Pmod ports of the Basys 3 seemingly stopped working, although the buttons and LEDs still worked. This problem disappeared the following day and never occurred again. Once this part of the project was working, design was started on the SD card driver. This began with the SD sending component, which was tested in simulation (Appendix I) and then with a simple test harness that sent a single command. Debugging this system took a significant amount of time because it was not known that data was supposed to be clocked out on the falling edge. Once this was solved, the component was turned into the SD command controller, which allowed a higher level driver to execute a series of commands to initialize the card. In this first phase, testing was done without any connection to the audio system. Once it was possible to fully initialize the SD card, work was begun to integrate it into the audio system. First, reading was implemented. Reading was deemed slightly easier than writing because there was no need to worry about erasing. In order to have something to read, a Python program was written to allow audio files to be written to an SD card in the format expected by the voice recorder (see Appendix J). The most difficult part of getting this to work was making sure the audio controller and SD driver stayed within the correct bounds of the buffer. Lastly, writing and erasing were implemented, which had similar issues as reading.

#### 3. Evaluation

Although the design goals were satisfied, there are a number of features that would almost certainly be necessary for this system to have any real applications or practicality. It is only capable of recording a single audio file, and new recording overwrites the previous recordings. A practical voice recorder needs to be able to store multiple recordings, ideally in a file system that is interoperable with other systems. The ability to store multiple recordings would also likely require a better user interface that provides more feedback to the user than just a few LEDs. It is not possible to swap SD cards without restarting the system, which is inconvenient. Many of the more complicated features are unsuited to an FPGA implementation, and would be much simpler to implement using a microprocessor.

## 4. Conclusions

The final design accomplished the initial goal of being able to record and play audio from the onboard RAM, as well as the secondary goal of writing that data to an SD card. The primary goal was easily achievable with the skills and resources obtained in ENGS 31. The SD card portion of the project was more difficult and required significant research outside of what was taught in class (How to Use MMC/SDC, 2018; SD Specifications, 2017). This meant that the TAs had limited ability to help with this part of the design. Students who want to implement an SD card driver in the future should be prepared to perform independent research and read technical specifications.

## 5. Acknowledgments

We gained the skills to implement this project from Professor Hansen's lectures and the laboratory exercises. In addition, our design process was facilitated in consultation with our learning fellow, Ella Ryan. The audio controller and the modifications to the A/D driver were done by Ben Wolsieffer. The D/A driver and the UI controller were written by Afia Semin. The SD card driver design and implementation were done by Ben Wolsieffer. The SD card portion of the project was outside the specifications as initially proposed at the design review.

# 6. References

"How to Use MMC/SDC." March 13, 2018. Accessed August 16, 2018.

http://elm-chan.org/docs/mmc/mmc\_e.html.

"SD Specifications Part 1: Physical Layer Simplified Specification." April 10, 2017. SD Association. Accessed August 12, 2018. https://www.sdcard.org/downloads/pls/.

# Appendix A - Annotated front panel

## Appendix B - Block diagrams

Figure B1. Hardware Block Diagram

Figure B2. Top level block diagram

Figure B3. D/A driver block diagram

Figure B4. Audio controller block diagram

Figure B5. UI controller block diagram

Figure B6. SD send component logic diagram

Figure B7. SD receive component logic diagram

Figure B8. Simplified block diagram for SD driver and command controller. This diagram shows basic data flows, but is missing many of the complicated implementation details.

# Appendix C - State diagrams<sup>2</sup>

Figure C1. D/A driver state diagram

<sup>&</sup>lt;sup>2</sup> To see enlarged versions of these diagrams, click on the image.

Figure C2. Audio controller state diagram

All outputs are zero if not specified.

Figure C3. UI controller state diagram

Figure C4. SD command controller state diagram

Figure C5. SD driver state diagram

# Appendix D - Parts list

| Quantity | Name      | Description                                            |

|----------|-----------|--------------------------------------------------------|

| 1        | Basys 3   | Xilinx Artix-7 FPGA development board                  |

| 1        | Pmod MIC3 | MEMS Microphone and 12-bit Analog-to-Digital convertor |

| 1        | Pmod DA2  | 2 channel 12-bit Digital-to-Analog converter           |

| 1        | Pmod AMP2 | Low power audio amplifier                              |

| 1        | Pmod SD   | Full-sized SD Card Slot                                |

| 1        | Speaker   | Speaker with male 3.5 mm jack                          |

## Appendix E - VHDL code and constraints

#### voice\_recorder.vhd

```

_____

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

-- Company: ENGS 31, 18X

-- Engineer: Ben Wolsieffer, Afia Semin

-- Create Date: 08/12/2018 08:28:03 PM

-- Design Name:

-- Module Name: voice_recorder - behavior

-- Project Name: VoiceRecorder

-- Target Devices: Basys 3

-- Tool Versions:

-- Description: Top level file for the voice recorder

_ _

-- Dependencies:

_ _

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

```

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

use IEEE.math_real.all;

entity voice_recorder is

port(mclk: in std_logic;

f_play_btn: in std_logic;

s_play_btn: in std_logic;

play_btn: in std_logic;

```

```

record btn: in std logic;

f play led: out std logic;

s play led: out std logic;

play led: out std logic;

record led: out std logic;

-- Data visualization

data leds: out std logic vector(11 downto 0);

ad spi sclk: out std logic;

ad spi sdata: in std logic;

ad spi cs: out std logic;

da spi sclk: out std logic;

da spi sdata: out std logic;

da spi cs: out std logic;

sd spi sclk: out std logic;

sd spi mosi: out std logic;

sd spi miso: in std logic;

sd spi cs: out std logic;

sd wp: in std logic;

sd cd: in std logic);

end voice recorder;

architecture behavior of voice recorder is

constant SCLK DIVIDER: positive := 10; -- 10 MHz

constant SAMPLE BITS: positive := 12;

-- number of bits in virtual address space used for counting

samples

constant INDEX BITS: positive := 32;

-- number of RAM address bits (RAM must be configured so entire

address space is addressable)

constant ADDR BITS: positive := 17;

component clock divider is

generic(divider: integer);

```

```

port(mclk: in std logic;

dclk: out std logic);

end component;

component down counter is

generic(bits: positive := 4);

port(clk: in std logic;

k: in std_logic_vector(bits - 1 downto 0); -- preset

value

CE: in std logic := '1'; -- count enable

preset: in std logic := '0'; -- assert to set the

counter to k

y: out std logic vector(bits - 1 downto 0); -- counter

output

TC: out std logic); -- terminal count

end component;

component pmod ad1 is

port(sclk: in std logic;

take sample: in std logic;

ad data: out std logic vector(11 downto 0) := (others =>

'0');

ad data ready: out std logic;

spi sclk: out std logic;

spi cs: out std logic;

spi sdata: in std logic);

end component;

component pmod da2

port(da data: in std logic vector (11 downto 0);

tick sample: in std logic;

sclk: in std logic;

spi data: out std logic;

spi sclk: out std logic;

spi cs: out std logic);

end component;

```

```

component UI controller

port(sclk: in std logic;

play btn: in std logic;

f play btn: in std logic;

s play btn: in std logic;

audio done: in std logic;

sd done: in std logic;

rec btn: in std logic;

play out: out std logic;

play led: out std logic;

f play led: out std logic;

s play led: out std logic;

rec out: out std logic;

rec led: out std logic;

tick sample div: out std logic vector(9 downto 0));

end component;

component sync is

port(clk: in std logic;

input: in std logic;

output: out std logic);

end component;

component audio controller is

generic(sample bits: positive := 12; -- sample depth in RAM

index bits: positive := 32;

addr_bits: positive := 17); -- width of RAM address

bus (must be fully addressable)

port(clk: in std logic;

-- UI signals

rec: in std_logic;

play: in std logic;

sd done: in std logic;

done: out std logic;

take sample: in std logic;

```

```

-- A/D

ad data: in std logic vector(11 downto 0);

ad data ready: in std logic;

ad take sample: out std logic;

-- D/A

da data: out std logic vector(11 downto 0);

da new sample: out std logic;

-- Address mapping information

index audio: out std logic vector(index bits - 1 downto

0); -- index of end of buffer/free space if recording or playing,

respectively (exclusive)

index sd: in std logic vector(index bits - 1 downto 0);

-- RAM

ram wr en: out std logic;

ram addr: out std logic vector(addr bits - 1 downto 0);

ram din: in std logic vector(sample bits - 1 downto 0);

ram dout: out std logic vector(sample bits - 1 downto

0));

end component;

component sd driver is

generic(sample bits: positive := 12; -- sample depth in RAM

index bits: positive := 40;

addr_bits: positive := 17); -- width of RAM address

bus (must be fully addressable)

port(sclk: in std logic;

rec: in std logic;

play: in std logic;

audio done: in std logic;

done: out std logic;

error: out std logic;

index audio: in std logic vector(index bits - 1 downto

0); -- location of audio controller in recordin

index sd: out std logic vector(index bits - 1 downto 0);

```

-- location of SD driver in recording

```

-- SD card

sd spi sclk: out std logic;

sd spi mosi: out std logic;

sd spi miso: in std logic;

sd spi cs: out std logic;

sd wp: in std logic;

sd cd: in std logic;

-- RAM

ram wr en: out std logic;

ram addr: out std logic vector(addr bits - 1 downto 0);

ram din: in std logic vector(sample bits - 1 downto 0);

ram dout: out std logic vector(sample bits - 1 downto

∂));

end component;

component audio buffer is

port(clka: in std logic;

wea: in std logic vector(0 downto 0);

addra: in std logic vector(16 downto 0);

dina: in std logic vector(11 downto 0);

douta: out std logic vector(11 downto 0);

clkb: in std logic;

web: in std logic vector(0 downto 0);

addrb: in std logic vector(16 downto 0);

dinb: in std logic vector(11 downto 0);

doutb: out std logic vector(11 downto 0));

end component;

component button is

generic(count: positive := 1000);

port(clk: in std logic;

input: in std logic;

output: out std logic);

end component;

```

```

-- clock used for SPI and all logic

signal sclk: std logic;

-- monopulsed buttons

signal s play btn mp, f play btn mp, play btn mp, record btn mp:

std logic := '0';

-- UI signals

signal rec, play, audio done, sd done, eof, sd error: std logic

:= '0';

signal take sample: std logic := '0';

signal tick sample div: std logic vector(9 downto 0) := (others

=> '0');

-- A/D signals

signal ad data: std logic vector(11 downto 0) := (others => '0');

signal ad data ready, ad take sample: std logic := '0';

-- D/A signals

signal da data: std logic vector(11 downto 0);

signal da new sample: std logic;

-- SD signals

signal sd wp sync: std logic;

signal index audio, index sd: std logic vector(INDEX BITS - 1

downto 0);

-- Audio RAM signals

signal audio ram wr en: std logic;

signal audio ram wr en vec: std logic vector(0 downto 0);

signal audio ram addr: std logic vector(ADDR BITS - 1 downto 0)

:= (others => '0');

signal audio ram din, audio ram dout:

std_logic_vector(SAMPLE_BITS - 1 downto 0) := (others => '0');

```

```

-- SD RAM signals

signal sd_ram_wr_en: std_logic;

signal sd_ram_wr_en_vec: std_logic_vector(0 downto 0);

signal sd_ram_addr: std_logic_vector(ADDR_BITS - 1 downto 0) :=

(others => '0');

signal sd_ram_din, sd_ram_dout: std_logic_vector(SAMPLE_BITS - 1

downto 0) := (others => '0');

```

#### begin

```

data_leds <= da_data;</pre>

-- sclk generator

sclk generator: clock divider

generic map(divider => SCLK DIVIDER)

port map(mclk => mclk,

dclk => sclk);

-- take sample generator

take sample counter: down counter

generic map(bits => 10)

port map(clk => sclk,

k => tick sample div,

TC => take sample);

-- A/D

ad: pmod ad1

port map(sclk => sclk,

take sample => ad take sample,

ad data => ad data,

ad data ready => ad data ready,

spi sclk => ad spi sclk,

spi sdata => ad spi sdata,

spi cs => ad spi cs);

-- D/A

da: pmod da2

port map(sclk => sclk,

```

```

tick sample => da new sample,

da data => da data,

spi sclk => da_spi_sclk,

spi data => da spi sdata,

spi cs => da spi cs);

-- play button debouncer

play btn debounce: button

port map(clk => sclk,

input => play btn,

output => play btn mp);

--fast play button debouncer

f play btn debounce: button

port map(clk => sclk,

input => f play btn,

output => f play btn mp);

-- slow play button debouncer

s play btn debounce: button

port map(clk => sclk,

input => s play btn,

output => s play btn mp);

-- record button debounce

record btn debounce: button

port map(clk => sclk,

input => record btn,

output => record btn mp);

-- UI controller

ui controller map: UI controller

port map(sclk => sclk,

play btn => play btn mp,

f play btn => f play btn mp,

s play btn => s play btn mp,

rec btn => record btn mp,

```

```

play_led => play_led,

```

```

f play led => f play led,

s play led => s play led,

rec led => record_led,

audio done => audio done,

sd done => sd done,

play out => play,

rec out => rec,

tick sample div => tick sample div);

-- port map main audio controller

audio controller map: audio controller

generic map(sample_bits => SAMPLE BITS,

index bits => INDEX_BITS,

addr bits => ADDR BITS)

port map(clk => sclk,

rec => rec,

play => play,

sd done => sd done,

done => audio done,

take sample => take sample,

ad data => ad data,

ad data ready => ad data ready,

ad take sample => ad take sample,

da data => da data,

da new sample => da new sample,

index audio => index audio,

index sd => index sd,

ram wr en => audio ram wr en,

ram addr => audio ram addr,

ram din => audio ram din,

ram dout => audio ram dout);

sd wp sync map: sync

port map(clk => sclk,

input => sd wp,

output => sd wp sync);

sd driver map: sd driver

```

```

generic map(sample bits => SAMPLE BITS,

index bits => INDEX BITS,

addr bits => ADDR BITS)

port map(sclk => sclk,

rec => rec,

play => play,

audio done => audio done,

done => sd done,

error => sd error,

index audio => index audio,

index sd => index sd,

sd spi sclk => sd spi sclk,

sd spi mosi => sd spi mosi,

sd spi miso => sd spi miso,

sd spi cs => sd spi cs,

sd_wp => sd_wp_sync,

sd cd => '1',

ram wr en => sd ram wr en,

ram addr => sd ram addr,

ram din => sd ram din,

ram dout => sd ram dout);

-- block RAM audio buffer

audio_ram_wr_en_vec(0) <= audio_ram_wr_en;</pre>

sd ram wr en vec(0) \le sd ram wr en;

ram: audio buffer

port map(clka => sclk,

```

wea => audio\_ram\_wr\_en\_vec, addra => audio\_ram\_addr, dina => audio\_ram\_dout, douta => audio\_ram\_din, clkb => sclk, web => sd\_ram\_wr\_en\_vec, addrb => sd\_ram\_addr, dinb => sd\_ram\_dout, doutb => sd\_ram\_din);

end behavior;

### pmod\_ad1.vhd

```

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

-- Company: ENGS 31, 18X

-- Engineer: Ben Wolsieffer

_ _

-- Create Date: 07/20/2018 09:27:40 AM

-- Design Name:

-- Module Name: pmod_ad1 - behavior

-- Project Name: pmod_ad1

-- Target Devices: Artix 7 - Basys 3

-- Tool Versions:

-- Description: Driver for the Diligent Pmod AD1 (Analog Devices

AD7476A).

_ _

-- Dependencies: down counter.vhd

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

_____

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity pmod_ad1 is

port(sclk: in std_logic;

take_sample: in std_logic;

ad_data: out std_logic_vector(11 downto 0) := (others =>

'0');

ad_data_ready: out std_logic;

spi sclk: out std logic;

spi_cs: out std_logic;

```

```

spi sdata: in std logic);

end pmod ad1;

architecture behavior of pmod ad1 is

component down counter is

generic(bits: positive := 4);

port (clk: in std logic;

k: in std logic vector(bits - 1 downto 0); -- preset

value

CE: in std logic := '1'; -- count enable

preset: in std logic := '0'; -- assert to set the

counter to k

y: out std logic vector(bits - 1 downto 0); -- counter

output

TC: out std logic); -- terminal count

end component;

-- Controller

type state type is (st wait, st shift, st load);

signal state: state type := st wait;

signal next state: state type := st wait;

-- Datapath

signal shift en: std logic := '0';

signal load en: std logic := '0';

signal ser data reg: std logic vector(11 downto 0) := (others =>

'0');

signal shift tc: std logic := '0';

signal shift preset: std logic := '0';

begin

-- Controller

shift counter: down counter port map(

clk => sclk,

k => std logic vector(to unsigned(14, 4)),

preset => shift preset,

TC => shift tc);

output proc: process(state) begin

```

```

shift en <= '0';</pre>

load en <= '0';</pre>

shift preset <= '0';</pre>

spi cs <= '1';</pre>

ad data ready <= '0';

case state is

when st wait => shift preset <= '1';</pre>

when st shift =>

shift en <= '1';</pre>

spi cs <= '0';</pre>

when st load =>

load en <= '1';</pre>

ad data ready <= '1';

end case;

end process;

next state proc: process(state, take sample, shift tc) begin

next state <= state;</pre>

case state is

when st wait =>

if take sample = '1' then

next state <= st shift;</pre>

end if;

when st shift =>

if shift tc = '1' then

next state <= st load;</pre>

end if;

when st load => next state <= st wait;</pre>

end case;

end process;

state update proc: process(sclk) begin

if rising edge(sclk) then

state <= next state;</pre>

end if;

end process;

```

```

-- Datapath

-- pass clock input to output

spi sclk <= sclk;</pre>

shift proc: process(sclk) begin

if rising edge(sclk) then

if shift en = '1' then

-- shift SPI data into the LSB

ser data reg <= ser data reg(ser data reg'high - 1</pre>

downto 0) & spi sdata;

end if;

end if;

end process;

load proc: process(sclk) begin

if rising edge(sclk) then

if load en = '1' then

-- copy 12 least significant bits from serial

register to A/D

-- data register

ad data <= ser data reg(ad data'range);</pre>

end if;

end if;

end process;

end behavior;

```

#### pmod\_da2.vhd

```

-- Target Devices: Artix 7 - Basys 3

-- Tool Versions:

-- Description: Driver for the Diligent Pmod DA2 (Texas Instruments

DAC1215101).

_ _

-- Dependencies:

_ _

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

_ _

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

entity pmod da2 is

port(da data: in std logic vector (11 downto 0);

tick sample: in std logic;

sclk: in std logic;

spi data: out std logic;

spi sclk: out std logic;

spi_cs: out std_logic);

end pmod da2;

architecture behavior of pmod_da2 is

signal n shifts: unsigned(3 downto 0):="1111";

signal shift en: std logic;

signal par_data_reg: std_logic_vector( 15 downto 0) := (others =>

'0');

signal TC: std logic;

signal iCS: std logic;

type state is (waits, load, shift);

signal curr state, next state: state;

```

```

begin

spi sclk <= sclk;</pre>

spi cs <= iCS;</pre>

shift count: process(sclk, n shifts, iCS) begin

if rising edge(sclk) then

if (n shifts > 0) and (iCS = '0') then

n shifts <= n shifts - 1;</pre>

elsif n shifts = "0000" then

n shifts <= "1111";</pre>

end if;

end if;

if n_shifts = "0000" then

TC <= '1';

else

TC <= '0';

end if;

end process shift count;

input reg: process(sclk, tick sample) begin

if rising edge(sclk) then

if tick sample = '1' then

par_data_reg <= std_logic_vector(resize(</pre>

unsigned(da data), 16));

elsif shift en <= '1' then</pre>

spi data <= par data reg(15);</pre>

par data reg <= par data reg(14 \text{ downto } 0) \& "0";

end if;

end if;

end process input reg;

state update: process(sclk) begin

if rising edge(sclk) then

curr state <= next state;</pre>

end if;

```

```

end process state_update;

controller: process(curr state, tick sample, TC) begin

iCS <= '1';

shift en <= '0';</pre>

next state <= curr state;</pre>

case curr_state is

when waits =>

iCS <= '1';

if tick sample = '1' then

next state <= load;</pre>

end if;

when load =>

next_state <= shift;</pre>

when shift =>

iCS <= '0';

shift en <= '1';</pre>

if TC = '1' then

next state <= waits;</pre>

end if;

end case;

end process controller;

```

```

end behavior;

```

### audio\_controller.vhd

-------- Company: ENGS 31, 18X -- Engineer: Ben Wolsieffer ---- Create Date: 08/11/2018 07:12:17 PM -- Design Name: -- Module Name: audio\_controller - behavior

```

-- Project Name: VoiceREcorder

-- Target Devices: Artix 7 - Basys 3

-- Tool Versions:

-- Description:

-- Dependencies:

_ _

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

_ _

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

use IEEE.math real.all;

entity audio_controller is

generic(sample bits: positive := 12; -- sample depth in RAM

index bits: positive := 40;

addr bits: positive := 17); -- width of RAM address bus

(must be fully addressable)

port(clk: in std logic;

-- UI signals

rec: in std logic;

play: in std logic;

sd done: in std logic;

done: out std logic;

take_sample: in std_logic;

-- A/D

ad_data: in std_logic_vector(11 downto 0);

ad data ready: in std logic;

ad take sample: out std logic;

```

```

-- D/A

da data: out std logic vector(11 downto 0);

da new sample: out std logic;

-- Address mapping information

index audio: out std logic vector(index bits - 1 downto 0);

-- index of end of buffer/free space if recording or playing,

respectively (exclusive)

index sd: in std logic vector(index bits - 1 downto 0);

-- RAM

ram wr en: out std logic;

ram addr: out std logic vector(addr bits - 1 downto 0);

ram din: in std logic vector(sample bits - 1 downto 0);

ram dout: out std logic vector(sample bits - 1 downto 0));

end audio controller;

architecture behavior of audio controller is

constant TAKE SAMPLE DIVIDER: integer := 20;

constant TAKE SAMPLE BITS: integer :=

integer(ceil(log2(real(TAKE SAMPLE DIVIDER))));

constant RAM_SIZE: positive := 2 ** addr_bits;

-- Maximum possible index

constant INDEX MAX: unsigned(index bits - 1 downto 0) := (others

=> '1');

component down counter is

generic(bits: positive := 4);

port (clk: in std logic;

k: in std logic vector(bits - 1 downto 0); -- preset

value

CE: in std logic := '1'; -- count enable

preset: in std logic := '0'; -- assert to set the

counter to k

y: out std logic vector(bits - 1 downto 0); -- counter

```

```

output

TC: out std logic); -- terminal count

end component;

type state type is (st idle, st record, st ad wait, st write,

st play, st index inc, st done);

type index sel type is (hold, increment, reset);

signal state: state type := st idle;

signal next state: state type;

signal index sel: index sel type;

signal rec end en: std logic;

signal da en: std logic;

signal index_reg: unsigned(INDEX_MAX'range) := (others => '0');

begin

ad take sample <= take sample;</pre>

da new sample <= take sample when da en = '1' else '0';</pre>

-- Take index modulo the RAM size, creating a circular buffer

ram addr <= std logic vector(index reg(ram addr'range));</pre>

ram dout <= ad data;</pre>

da data <= ram din;</pre>

-- Update address register

index reg proc: process(clk) begin

if rising edge(clk) then

case index sel is

when hold => null;

when increment => index reg <= index reg + 1;</pre>

when reset => index reg <= (others => '0');

end case;

end if;

end process;

```

```

index_audio <= std_logic_vector(index_reg);</pre>

```

```

next state proc: process(state, index reg, play, rec,

take sample, ad data ready, sd done, index sd)

variable index sd end: unsigned(index sd'range); -- end of

free RAM space while recording

begin

-- Calculate end of free space (only used when recording)

if unsigned(index sd) > INDEX MAX - RAM SIZE then

index sd end := INDEX MAX;

else

index sd end := unsigned(index sd) + RAM SIZE;

end if;

next state <= state;</pre>

case state is

when st idle =>

if rec = '1' then

next state <= st record;</pre>

elsif play = '1' then

next state <= st play;</pre>

end if;

-- Record

when st_record =>

if rec = '0' or sd done = '1' then

next state <= st done;</pre>

elsif take sample = '1' and index reg < index sd end</pre>

then

-- only record when there is free space

next state <= st ad wait;</pre>

end if;

when st ad wait =>

if ad data ready = '1' then

next state <= st write;</pre>

end if;

when st_write =>

if index reg = INDEX MAX then

-- If we run out of indices, stop.

-- Must be checked after sample has been taken,

```

```

-- an overflow can occur

next state <= st done;</pre>

else

next state <= st record;</pre>

end if;

-- Play

when st play =>

if play = '0' then

next state <= st done;</pre>

elsif index reg + 1 < unsigned(index sd) then</pre>

-- only play when there are samples in the buffer

if take sample = '1' then

next state <= st index inc;</pre>

end if;

elsif sd done = '1' then

-- if the sd card has finished buffering and we

reach

-- the end of the buffer, we are done

next state <= st done;</pre>

end if;

when st_index_inc => next_state <= st_play;</pre>

when st done =>

if sd_done = '1' then

next state <= st idle;</pre>

end if;

end case;

end process;

output proc: process(state) begin

index sel <= reset;</pre>

rec end en <= '0';</pre>

da en <= '0';</pre>

ram_wr_en <= '0';</pre>

done <= '0';

case state is

```

```

when st idle => null;

when st record =>

index sel <= hold;</pre>

when st_ad_wait =>

index sel <= hold;</pre>

when st write =>

ram wr en <= '1';</pre>

index sel <= increment;</pre>

rec_end_en <= '1';</pre>

when st play =>

index sel <= hold;</pre>

da en <= '1';</pre>

when st index inc =>

index sel <= increment;</pre>

when st done =>

done <= '1';</pre>

end case;

end process;

state update proc: process(clk) begin

if rising_edge(clk) then

state <= next state;</pre>

end if;

end process;

```

end behavior;

## UI\_controller.vhd

```

-- Target Devices: Artix 7 - Basys 3

-- Tool Versions:

-- Description:

_ _

-- Dependencies:

- -

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

use IEEE.math real.all;

entity UI controller is

port(sclk: in std logic;

play btn: in std logic;

f play btn: in std logic;

s_play_btn: in std_logic;

audio done: in std logic;

sd done: in std logic;

rec btn: in std logic;

play out: out std logic;

play led: out std logic;

f play led: out std logic;

s_play_led: out std_logic;

rec_out: out std_logic;

rec led: out std logic;

tick sample div: out std logic vector(9 downto 0));

end UI controller;

```

architecture Behavioral of UI\_controller is

```

constant TAKE_SAMPLE_BITS: integer := 10;

```

```

constant TAKE_SAMPLE_DIVIDER: integer := 227; -- 44.052 kHz

constant F_TAKE_SAMPLE_DIVIDER: integer := 114; -- 87.719 kHz

constant S_TAKE_SAMPLE_DIVIDER: integer := 600; -- 16.667 kHz

```

```

type state is (idle, play, fast_play, slow_play, rec, done_wait);

signal curr_state, next_state: state;

```

## begin

```

controller: process(curr state, f play btn, s play btn, play btn,

rec btn, audio done, sd done) begin

play out <= '0';</pre>

play led <= '0';</pre>

f play led <= '0';</pre>

s play led <= '0';</pre>

rec out <= '0';</pre>

rec led <= '0';</pre>

tick sample div <=</pre>

std logic vector(to unsigned(TAKE SAMPLE DIVIDER, TAKE SAMPLE BITS));

next state <= curr state;</pre>

case curr state is

when idle =>

if play btn = '1' then

next state <= play;</pre>

end if;

if f play btn = '1' then

next state <= fast play;</pre>

end if;

if s play btn = '1' then

next state <= slow play;</pre>

end if;

if rec btn = '1' then

```

```

next state <= rec;</pre>

end if;

when play =>

play out <= '1';</pre>

play led <= '1';</pre>

if audio_done = '1' and sd_done = '1' then

next state <= idle;</pre>

elsif play btn = '1' then

next state <= done wait;</pre>

end if;

when fast play =>

play out <= '1';</pre>

f play led <= '1';</pre>

tick sample div <=</pre>

std_logic_vector(to_unsigned(F_TAKE_SAMPLE_DIVIDER,

TAKE SAMPLE BITS));

if audio done = '1' and sd done = '1' then

next state <= idle;</pre>

elsif f play btn = '1' then

next state <= done wait;</pre>

end if;

when slow play =>

play out <= '1';</pre>

s play led <= '1';</pre>

tick sample div <=</pre>

std logic vector(to unsigned(S TAKE SAMPLE DIVIDER,

TAKE SAMPLE BITS));

if audio done = '1' and sd done = '1' then

next state <= idle;</pre>

elsif s play btn = '1' then

next state <= done wait;</pre>

end if;

when rec =>

rec out <= '1';</pre>

```

```

rec led <= '1';</pre>

if audio done = '1' and sd done = '1' then

next state <= idle;</pre>

elsif rec btn = '1' then

next state <= done wait;</pre>

end if;

when done wait =>

if audio_done = '1' and sd_done = '1' then

next state <= idle;</pre>

end if;

end case;

end process;

state_update: process(sclk) begin

if rising edge(sclk) then

curr_state <= next_state;</pre>

end if;

end process state update;

end Behavioral;

sd driver.vhd

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

-- Company: ENGS 31, 18X

-- Engineer: Ben Wolsieffer

```

- -- Create Date: 08/14/2018 04:27:27 PM

- -- Design Name:

- -- Module Name: sd\_driver behavior

- -- Project Name:

- -- Target Devices:

- -- Tool Versions:

- -- Description:

```

- -

```

-- Dependencies: sd\_cmd.vhd

```

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

```

```

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

use IEEE.math real.all;

entity sd driver is

generic(sample bits: positive := 12; -- sample depth in RAM

index bits: positive := 40;

addr bits: positive := 17); -- width of RAM address bus

(must be fully addressable)

port(sclk: in std logic;

rec: in std logic;

play: in std logic;

audio done: in std logic;

done: out std logic;

error: out std_logic;

index audio: in std logic vector(index bits - 1 downto 0);

-- location of audio controller in recordin

index sd: out std logic vector(index bits - 1 downto 0); --

location of SD driver in recording

-- SD card

```

sd\_spi\_sclk: out std\_logic; sd\_spi\_mosi: out std\_logic; sd\_spi\_miso: in std\_logic; sd\_spi\_cs: out std\_logic; sd\_wp: in std\_logic; sd cd: in std logic;

```

-- RAM

ram wr en: out std logic;

ram addr: out std logic vector(addr bits - 1 downto 0);

ram din: in std logic vector(sample bits - 1 downto 0);

ram dout: out std logic vector(sample bits - 1 downto 0));

end sd driver;

architecture behavior of sd driver is

constant SECTOR SIZE: positive := 512;

-- don't start at beginning of device

constant SECTOR OFFSET: natural := 8192;

constant ADDR OFFSET: natural := SECTOR OFFSET * SECTOR SIZE;

-- hardcoded erase block size

constant ERASE SECTORS: positive := 8192;

constant BYTES PER INDEX: positive := 2;

constant INDICES_PER_SECTOR: positive := SECTOR SIZE /

BYTES PER INDEX;

constant RAM_SIZE: positive := 2 ** addr_bits;

-- Maximum possible index

constant INDEX MAX: unsigned(index bits - 1 downto 0) := (others

=> '1');

component down counter is

generic(bits: positive := 4);

port(clk: in std logic;

k: in std logic vector(bits - 1 downto 0); -- preset

value

CE: in std logic := '1'; -- count enable

preset: in std logic := '0'; -- assert to set the

counter to k

y: out std logic vector(bits - 1 downto 0); -- counter

```

output

```

TC: out std logic); -- terminal count

end component;

component sd cmd is

port(sclk: in std logic;

cmd: in std logic vector(5 downto 0);

cmd arg: in std logic vector(31 downto 0);

cmd start: in std logic; -- assert to start command

cmd end: out std logic;

res r1: out std logic vector(7 downto 0) := x"00"; -- r1

response (first byte of response)

res data: out std logic vector(31 downto 0) :=

x"00000000"; -- response data/card status

data index: out std logic vector(8 downto 0);

data in: in std logic vector(7 downto 0);

data out: out std logic vector(7 downto 0);

data out en: out std logic;

error: out std logic;

sd spi sclk: out std logic;

sd spi mosi: out std logic;

sd spi miso: in std logic;

sd spi cs: out std logic);

end component;

type state type is (start, init, go idle state, send if cond,

app cmd, sd send op cond, read ocr, set blocklen, send csd,

idle, st done, st error,

st play, read length, read samples,

play sector inc,

st record, write samples, record sector inc,

erase wr blk start addr, erase wr blk end addr, erase, write length);

signal state: state type := start;

signal next state: state type;

signal sd init: std logic;

-- Command type and argument registers

```

```

signal cmd: std logic vector(5 downto 0);

signal cmd_arg: std_logic_vector(31 downto 0);

signal cmd start, cmd end: std logic;

-- Response data

signal res r1: std logic vector(7 downto 0);

signal res data: std logic vector(31 downto 0);

-- Data block

signal data index: std logic vector(8 downto 0);

signal data in, data out: std logic vector(7 downto 0);

signal data out en: std logic;

type read dest type is (dest length, dest ram, dest csd);

signal read dest: read dest type;

signal cmd error: std logic;

-- card information

-- card specific data (CSD)

subtype CSD STRUCTURE is natural range 127 downto 126;

subtype CSD V1 READ BL LEN is natural range 83 downto 80;

subtype CSD V1 C SIZE is natural range 73 downto 62;

subtype CSD V1 C SIZE MULT is natural range 49 downto 47;

subtype CSD V2 C SIZE is natural range 69 downto 48;

signal csd reg: std logic vector(127 downto 0) := (others =>

'0');

-- maximum sector index (from CSD)

signal card sector max: unsigned(31 downto 0);

-- operation conditions register (indicates that card is SDHC or

SDXC)

constant OCR CCS: natural := 30;

signal ocr reg: std logic vector(31 downto 0);

signal ocr reg en: std logic;

```

```

-- Audio information

-- current sector

signal sector: unsigned(31 downto 0) := (others => '0');

signal addr: unsigned(40 downto 0);

signal sector_reset, sector_inc: std_logic;

signal sector_multiplier: unsigned(9 downto 0);

-- index: logical index in the audio file

signal index: unsigned(index_bits - 1 downto 0);

-- maximum logical index of recorded data

-- stored in first bytes of card (little endian)

signal index_end: unsigned(index_bits - 1 downto 0) := (others => '0');

```

# begin

```

init counter: down counter

generic map(bits => 8)

port map(clk => sclk,

k => x''64'',

TC => sd init);

sd cmd map: sd cmd

port map(sclk => sclk,

cmd => cmd,

cmd arg => cmd arg,

cmd start => cmd start,

cmd end => cmd end,

res r1 => res r1,

res data => res data,

data index => data index,

data in => data in,

data out => data out,

data out en => data out en,

error => cmd error,

```

```

sd spi sclk => sd spi sclk,

sd spi mosi => sd spi mosi,

sd spi miso => sd spi miso,

sd spi cs => sd spi cs);

ocr proc: process(sclk) begin

if rising edge(sclk) then

if ocr reg en = '1' then

ocr reg <= res data;</pre>

end if;

end if;

end process;

read dest proc: process(sclk, index, index end, data index,

read dest, ram din, data out, data out en)

variable bit_low: natural;

variable unwrapped index: unsigned(index'range);

begin

bit low := to integer(unsigned(data index)) * 8;

ram wr en <= '0';</pre>

ram dout <= (others => '0');

data in <= (others => '0');

-- Every 12 bit sample is stored in two bytes on the SD card

unwrapped index := index + unsigned(data index) /

BYTES PER INDEX;

ram addr <=

std logic vector(unwrapped index(ram addr'range));

case read dest is

when dest ram =>

ram wr en <= data out en;</pre>

if data index(0) = '0' then -- even

data in <= ram din(3 downto 0) & "0000";</pre>

ram dout <= "00000000" & data out(7 downto 4);</pre>

else -- odd

data in <= ram din(11 downto 4);</pre>

```

```

ram dout <= data out & ram din(3 downto 0);</pre>

end if;

when dest length =>

if unsigned(data index) < 4 then

data in <= std logic vector(index(bit low + 7</pre>

downto bit low));

end if;

when others => null;

end case;

if rising edge(sclk) then

if data out_en = '1' then

case read_dest is

when dest length =>

if unsigned(data index) < 4 then</pre>

index end(bit low + 7 downto bit low) <=</pre>

unsigned(data out);

end if;

when dest csd => csd reg(bit low + 7 downto

bit low) <= data out;</pre>

when others => null;

end case;

end if;

end if;

end process;

card size proc: process(csd reg) begin

if csd reg(CSD STRUCTURE) = "00" then

-- SD v1.xx or MMC

card sector max <=

(resize(unsigned(csd reg(CSD V1 C SIZE)), card sector max'length) +

1) sll

(to integer(unsigned(csd reg(CSD V1 C SIZE MULT))) +

2 + to integer(unsigned(csd reg(CSD V1 READ BL LEN))) / SECTOR SIZE);

else

--SD >= v2.00

card sector max <=

resize(unsigned(csd_reg(CSD_V2_C_SIZE)) * 1024 + 1023,

```

```

card sector max'length);

end if;

end process;

sector proc: process(sclk) begin

if rising edge(sclk) then

if sector reset = '1' then

sector <= to unsigned(SECTOR OFFSET, sector'length);</pre>

elsif sector inc = '1' then

sector <= sector + 1;

end if;

end if;

end process;

sector_multiplier <= "000000001" when ocr_reg(OCR_CCS) = '1'</pre>

else "1000000000";

index <= resize((sector - SECTOR OFFSET) * INDICES PER SECTOR,</pre>

index'length);

addr <= resize(sector * SECTOR_SIZE, addr'length);</pre>

index sd <= std logic vector(index);</pre>

next state proc: process(state, sd init, play, rec, cmd end,

cmd error, res r1, res data, index audio, index, index end, sector,

card sector max, audio done, sd wp)

variable index audio end: unsigned(index sd'range); -- end of

free RAM space during playback

begin

-- Calculate end of free space (only used when playing)

if unsigned(index audio) > INDEX MAX - RAM SIZE then

index audio end := INDEX MAX;

else

index audio end := unsigned(index audio) + RAM SIZE;

end if;

next state <= state;</pre>

case state is

```

```

when start => next state <= init;</pre>

when init =>

if sd init = '1' then

next state <= go idle state;</pre>

end if;

when idle =>

if play = '1' then

next state <= read length;</pre>

elsif rec = '1' then

next state <= st record;</pre>

end if;

when st play =>

-- the index conditions are also checked in

play sector inc.

-- They are checked here in the unlikely case that

they are

-- violated before the recording even begins (very

short

-- recording, card smaller than the offset), but they

must also

-- be checked before the increment occurs to prevent

wrapping

-- with the largest cards and recordings.

if play = '0' or index + (INDICES PER SECTOR - 1) >

index end or sector > card sector max then

next state <= st done;</pre>

elsif index audio end > index + (INDICES PER SECTOR -

1) then

next state <= read samples;</pre>

end if;

when play sector inc =>

-- handle reaching the end of the recording, running

out of SD

-- card space, or reaching the maximum index. These

must be

-- handled before they occur to avoid a possible

overflow, but

-- after the samples for the sector have been read.

```

```

if index + (INDICES PER SECTOR - 1) >= index end or

sector >= card sector max then

next state <= st done;</pre>

else

next state <= st play;</pre>

end if;

when st record =>

-- Like playback, we should handle the boundary

conditions both

-- here and in record sector inc

if sd wp = '1' then

next state <= st done;</pre>

elsif sector > card sector max then

next state <= write length;</pre>

elsif unsigned(index audio) > index +

(INDICES PER SECTOR - 1) then

if (sector mod ERASE SECTORS) = 0 then

next state <= erase wr blk start addr;</pre>

else

next state <= write samples;</pre>

end if;

elsif audio done = '1' then

next state <= write length;</pre>

end if:

when record sector inc =>

if sector >= card sector max then

next state <= write length;</pre>

else

next state <= st record;</pre>

end if;

when st done =>

if audio done = '1' then

next state <= idle;</pre>

end if;

when st error => null;

when others =>

if cmd end = '1' then

case state is

```

```

when go idle state =>

if res_r1 = x''01'' then

next state <= send if cond;</pre>

end if;

when send if cond =>

if res data(11 downto 0) = x"1AA" then

next state <= app cmd;</pre>

else

next state <= st error;</pre>

end if;

when app cmd =>

next_state <= sd_send_op_cond;</pre>

when sd_send_op_cond =>

if res r1 = x''01'' then

-- retry ACMD41

next state <= app cmd;</pre>

else

next state <= read ocr;</pre>

end if;

when read ocr =>

if res data(OCR CCS) = '1' then

next_state <= send_csd;</pre>

else

next_state <= set_blocklen;</pre>

end if;

when set blocklen => next state <= send csd;</pre>

when send csd => next state <= idle;</pre>

when read length => next state <= st play;</pre>

when read samples => next state <=

play_sector_inc;

when write samples => next state <=

record_sector_inc;

when erase_wr_blk_start_addr => next_state <=</pre>

erase wr blk end addr;

when erase wr blk end addr => next state <=

erase;

when erase => next state <= write samples;</pre>

when write length => next state <= st done;</pre>

```

```

when others => null;

end case;

end if;

end case;

-- error catching

if cmd error = '1' then

next_state <= st_error;</pre>

end if;

end process;

output proc: process(state, sector, sector multiplier) begin

done <= '0';</pre>

error <= '0';</pre>

sector reset <= '0';</pre>

sector inc <= '0';</pre>

ocr reg en <= '0';</pre>

cmd start <= '0';</pre>

cmd <= "000000";</pre>

cmd arg <= x"00000000";</pre>

read dest <= dest ram;</pre>

case state is

when start => null;

when init => null;

when idle => sector_reset <= '1';</pre>

when st play => null;

when play sector inc => sector inc <= '1';</pre>

when st record => null;

when record sector inc => sector inc <= '1';</pre>

when st done => done <= '1';</pre>

when st error => error <= '1';</pre>

when others =>

cmd start <= '1';</pre>

case state is

when go idle state => null;

when send if cond =>

cmd <= "001000";</pre>

```

```

cmd arg <= x"000001AA";</pre>

when app cmd =>

cmd <= "110111";</pre>

when sd send op cond =>

cmd <= "101001";</pre>

cmd arg <= x"40000000";</pre>

when read ocr =>

cmd <= "111010";</pre>

ocr reg en <= '1';</pre>

when set blocklen =>

cmd <= "010000";</pre>

cmd arg <= x''00000200'';

when send csd =>

cmd <= "001001";</pre>

read dest <= dest csd;</pre>

when read_length =>

cmd <= "010001";</pre>

read dest <= dest length;</pre>

when read samples =>

cmd <= "010001";</pre>

cmd arg <= std logic vector(resize(sector *</pre>

sector multiplier, cmd arg'length));

read dest <= dest ram;</pre>

when write samples =>

cmd <= "011000";</pre>

cmd arg <= std logic vector(resize(sector *</pre>

sector multiplier, cmd arg'length));

read dest <= dest ram;</pre>

when erase wr blk start addr =>

cmd <= "100000";</pre>

cmd arg <= std logic vector(resize((sector +</pre>

ERASE_SECTORS) * sector_multiplier + ERASE_SECTORS, cmd_arg'length));

when erase wr blk end addr =>

cmd <= "100001";</pre>

cmd arg <= std logic vector(resize((sector +</pre>

ERASE_SECTORS - 1) * sector_multiplier, cmd_arg'length));

when erase =>

cmd <= "100110";</pre>

```

### end behavior;

### sd\_cmd.vhd

\_\_\_\_\_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ -- Company: ENGS 31, 18X -- Engineer: Ben Wolsieffer \_ \_ -- Create Date: 08/14/2018 04:27:27 PM -- Design Name: -- Module Name: sd cmd - behavior -- Project Name: VoiceRecordr -- Target Devices: -- Tool Versions: -- Description: \_ \_ -- Dependencies: sd\_send.vhd, sd\_recv.vhd, down\_counter.vhd \_ \_ -- Revision: -- Revision 0.01 - File Created -- Additional Comments:  library IEEE; use IEEE.std logic 1164.all; use IEEE.numeric std.all; use IEEE.math real.all; entity sd cmd is port(sclk: in std logic; cmd: in std logic vector(5 downto 0); cmd arg: in std logic vector(31 downto 0); cmd start: in std logic; -- assert to start command cmd end: out std logic; res r1: out std logic vector(7 downto 0) := x"00"; -- r1 response (first byte of response) res data: out std logic vector(31 downto 0) := x"00000000"; -- response data/card status data index: out std logic vector(8 downto 0); data in: in std logic vector(7 downto 0); data out: out std logic vector(7 downto 0); data out en: out std logic; error: out std logic; sd spi sclk: out std logic; sd spi mosi: out std logic; sd spi miso: in std logic; sd spi cs: out std logic); end sd cmd; architecture behavior of sd cmd is constant CMD LENGTH: integer := 7; constant CMD INDEX BITS: integer := integer(ceil(log2(real(CMD LENGTH)))); component down counter is generic(bits: positive := 4); port(clk: in std logic; k: in std logic vector(bits - 1 downto 0); -- preset

\_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_

value CE: in std logic := '1'; -- count enable preset: in std\_logic := '0'; -- assert to set the counter to k y: out std logic vector(bits - 1 downto 0); -- counter output TC: out std logic); -- terminal count end component; component sd send is generic(bits: positive := 8); port(clk: in std logic; data: in std logic vector(bits - 1 downto 0); -- data to send to card new data: in std logic; -- data is registered on rising edae when asserted done: out std logic; -- when asserted, the previously registered data has been processed spi mosi: out std logic := '0'; spi cs: out std logic := '1'); end component; component sd recv is generic(bits: positive := 8); port(clk: in std logic; data: out std logic vector(bits - 1 downto 0); -- data to send to card new data: out std logic; -- asserted when new data available on next rising edge, cleared after get\_data asserted spi miso: in std logic := '0'); end component; type state type is (idle, cmd load, send wait, -- send command res wait, recv wait, res data load, -receive response data token wait, data read wait, data read load, -- read data block

```

data token load, data write load,

data write wait, data response wait, -- write data block

busy wait, done, sd error);

signal state: state type := idle;

signal next_state: state_type;

type send data src type is (src cmd, src data in,

src data token);

signal send data src: send data src type;

signal send data: std logic vector(7 downto 0);

signal send done, send new data: std logic;

signal recv data: std logic vector(7 downto 0);

signal recv data block, recv done: std logic;

-- Command type and argument registers

signal cmd reg: unsigned(cmd'range);

signal cmd_arg_reg: std_logic_vector(cmd arg'range);

signal cmd reg en: std logic;

signal cmd index vec: std logic vector(CMD INDEX BITS - 1 downto

0);

signal cmd index: unsigned(cmd index vec'range);

signal cmd index preset, cmd index inc, cmd done: std logic;

signal cmd data: std logic vector(55 downto 0);

-- Response data

signal res max index: std logic vector(3 downto 0);

signal res index vec: std logic vector(res max index'range);

signal res index: unsigned(res index vec'range);

signal res index preset, res index inc, res r1 en, res data en,

res done: std logic;

-- Data block

signal data index reset, data index inc: std logic;

signal data index reg, data index max: unsigned(9 downto 0) :=

```

```

(others => '0');

```

### begin

```

sd spi sclk <= sclk;</pre>

send: sd send

port map(clk => sclk,

data => send data,

new data => send new data,

done => send done,

spi mosi => sd spi mosi,

spi cs => sd spi cs);

recv: sd recv

port map(clk => sclk,

data => recv data,

new data => recv done,

spi miso => sd spi miso);

cmd index <= unsigned(cmd index vec);</pre>

cmd index counter: down counter

generic map(bits => CMD INDEX BITS)

port map(clk => sclk,

k => std logic vector(to unsigned(CMD LENGTH - 1,

CMD INDEX BITS)),

CE => cmd index inc,

preset => cmd index preset,

y => cmd index vec,

TC => cmd done);

cmd reg update: process(sclk) begin

if rising edge(sclk) then

if cmd reg en = '1' then

cmd reg <= unsigned(cmd);</pre>

cmd arg reg <= cmd arg;</pre>

end if;

end if;

end process;

```

```

cmd data proc: process(cmd reg, cmd arg reg)

variable crc: std logic vector(6 downto 0);

begin

-- Only CMD0 and CMD8 actually require CRC unless it is

explicitly

-- enabled. Rather than calculate it, we use hardcoded values

assumina

-- the argument will always be the same.

if cmd reg = 0 then

-- arg is 0x0000000

crc := "1001010";

elsif cmd reg = 8 then

-- arg is 0x000001AA

crc := "1000011";

else

crc := "0000000";

end if;

-- some cards apparently like having a 0xFF byte ahead of the

command (after CS is asserted)

cmd_data <= x"FF" & "01" & std_logic_vector(cmd_reg) &</pre>

cmd arg reg & crc & "1";

end process;

send data proc: process(send data src, cmd index, cmd data,

data index reg, data index max, data in)

variable addr low: integer;

begin

addr low := to integer(cmd index) * 8;

case send data src is

when src cmd => send data <= cmd data(addr low + 7 downto

addr low);

when src data in =>

if data index reg < data index max - 1 then

send data <= data in;</pre>

else

-- Last two bytes are a dummy CRC

```

```

send data <= x"00";</pre>

end if;

when src data token => send data <= x"FE";</pre>

end case;

end process;

res max index proc: process(cmd reg) begin

-- calculate response length

case to integer(cmd reg) is

when 8 | 41 | 58 =>

res max index <= x"3";</pre>

when others =>

res max index <= x"0";</pre>

end case;

end process;

res index <= unsigned(res index vec);</pre>

res index counter: down counter

generic map(bits => res index'length)

port map(clk => sclk,

k => res max index,

CE => res index inc,

preset => res index preset,

y => res index vec,

TC => res done);

res r1 proc: process(sclk) begin

if rising edge(sclk) then

if res r1 en = '1' then

res r1 <= recv data;</pre>

end if;

end if;

end process;

res data proc: process(sclk, res index)

variable addr low: integer;

begin

addr low := to integer(res index) * 8;

```

```

if rising edge(sclk) then

if res data en = '1' then

res data(addr low + 7 downto addr low) <= recv data;</pre>

end if;

end if;

end process;

data index max proc: process(cmd reg) begin

case to integer(cmd reg) is

when 17 | 18 | 24 | 25 => data index max <= "1000000001";

-- 513 (512 bytes + CRC)

when 9 | 10 => data index max <= "0000010001"; -- 17 (16

bytes + CRC)

when others => data index max <= (others => '0');

end case;

end process;

data index counter: process(sclk, data index reset,

data index inc) begin

if rising edge(sclk) then

if data index reset = '1' then

data index reg <= (others => '0');

elsif data index inc = '1' then

data index reg <= data index reg + 1;</pre>

end if;

end if;

end process;

-- Truncate index register and send it to output. This will wrap

around when

-- it reaches the CRC (which the user doesn't care about), but

data out en

-- will not be asserted, so users should ignore it.

data index <= std logic vector(data index reg(data index'range));</pre>

-- send received data directly to data out

-- should only be assumed to be valid when data out en is

asserted

```

data\_out <= recv\_data;</pre>

```

next state proc: process(state, cmd reg, cmd start, cmd done,

send done, recv data, recv done, res done, data index reg,

data index max) begin

next state <= state;</pre>

case state is

when idle =>

if cmd start = '1' then

next state <= cmd load;</pre>

end if;

when cmd load =>

if cmd done = '1' then

next state <= res wait;</pre>

else

next state <= send wait;</pre>

end if;

when send_wait =>

if send done = '1' then

next state <= cmd load;</pre>

end if;

when res wait =>

if recv data /= x"FF" then

-- ignore idle state bit in determining if there

was an error

if (recv data and x"FE") = x"00" then

next state <= recv wait;</pre>

else

next state <= sd error;</pre>

end if;

end if;

when recv wait =>

if recv done = '1' then

next state <= res data load;</pre>

end if;

when res data load =>

if res done = '1' then

case to integer(cmd reg) is

-- commands that have data block

```

```

when 9 | 10 | 17 => next state <=

data token wait;

when 24 => next state <= data token load;</pre>

-- responses possibly have a busy signal

after them

when others => next state <= busy wait;</pre>

end case;

else

next state <= recv wait;</pre>

end if;

when data token wait =>

if recv data = x"FE" then

next state <= data read wait;</pre>

end if;

when data read wait =>

if recv done = '1' then

next state <= data read load;</pre>

end if;

when data read load =>

if data index reg = data index max then

next state <= done;</pre>

else

next state <= data read wait;</pre>

end if;

when data token load => next state <= data write wait;</pre>

when data write wait =>

if send done = '1' then

next state <= data write load;</pre>

end if;

when data write load =>

if data index reg = data index max then

next state <= data response wait;</pre>

else

next state <= data write wait;</pre>

end if;

when data response wait =>

if recv data(4 downto 0) = "00101" then

-- correct response, wait for busy signal to end

```

```

next state <= busy wait;</pre>

elsif recv data /= x"FF" then

-- got response, but it was not what was expected

next state <= sd error;</pre>

end if;

when busy wait =>

if recv data = x"FF" then

next state <= done;</pre>

end if;

when done => next state <= idle;</pre>

when sd error => next state <= idle;</pre>

end case;

end process;

output proc: process(state, data index reg, data index max) begin

cmd reg en <= '0';</pre>

cmd index preset <= '0';</pre>

cmd index inc <= '0';</pre>

send new data <= '0';</pre>

res index preset <= '0';</pre>

res index inc <= '0';</pre>

res r1 en <= '0';</pre>

res data en <= '0';</pre>

data index reset <= '0';</pre>

data index inc <= '0';</pre>

data out en <= '0';</pre>

send data src <= src cmd;</pre>

cmd end <= '0';</pre>

error <= '0';</pre>

case state is

when idle =>

cmd reg en <= '1';</pre>

cmd index preset <= '1';</pre>

when cmd_load =>

cmd index inc <= '1';</pre>

send new data <= '1';</pre>

when send wait => null;

```

```

when res wait =>

res index preset <= '1';</pre>